## Quiz #3

May 28, 2007 Prof. Woo-Young Choi Electronic Circuits II

## Problem 1 (4)

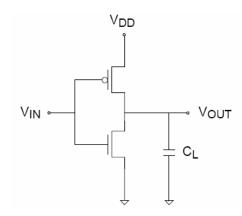

Consider the following CMOS inverter having  $v_{Tn}$ =1V,  $v_{Tp}$ = -1V,  $V_{DD}$  = 2.5V,  $r_{on}$  =  $r_{op}$  = 50K $\Omega$ , and k'(W/L)=1mA/V<sup>2</sup> for both NMOS and PMOS transistors.

Estimate the noise margin for the low logic level.

## Problem 2 (3)

Draw the transistor-level circuit configuration for CMOS XOR gate. Assume the input signals are available in A, A, B and B.

## <u>Problem 3 (3)</u>

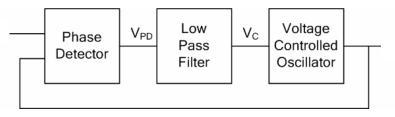

Consider the following block diagram for PLL.

Assume the phase detector has gain of  $K_{PD}$ , the VCO has gain of  $K_{VCO}$ , and the low pass filter has one pole at  $\omega_p$ . Derive the close-loop transfer function in s-domain for  $\phi_{out}/\phi_{in}$ .